БГУИР ВМСИС 2014

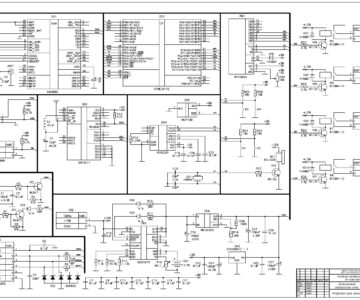

Тип архитектуры: принстонская

Шина данных разрядностью 8 бит

Адресная шина разрядностью 12 бит

ОЗУ: синхронная

ПЗУ: асинхронная

Тип адресации: непосредственная

РОН: 20шт

Кеш k=2

Алгоритм замещения: без анализа

Синхронизация с памятью: флажковоотложенная

АЛУ: ADDC

Логические коды: NOT, AND

Сдвиговый код: ROR

Арбитаж: центрально-параллельный

Стек, обьем роста: 12/вниз

Схема предсказания переходов: А2

Помимо указанных в таблице команд, реализованы обязательные команды:

MOV adr, reg; MOV reg, adr; JMP adr; PUSH reg, POP reg, HLT, а так же DMA (прямой доступ к памяти) в 2-ух вариантах: кэшируемый и некэшируемый.

При реализации АЛУ и УУ был так же реализован регистр флагов FR.

Архитектура принстонская, следовательно, шина для ROM и RAM будет общая, что нужно учитывать при разработке операций. При непосредственной адресации операнд располагается в адресном поле команды (ROM). Пример: mov ax, 40h

Количество регистров общего назначения – 20шт.

Тип КЭШ-памяти – с множественно-ассоциативным отображением (k = 2)

Алгоритм замещения строк – без анализа, что упрощает разработку (но уменьшает эффективность КЭШа).Тип синхронизации КЭШа с памятью один из самых сложных (если не самый) – флаговая отложенная синхронизация.

Операции АЛУ тривиальны, их нужно будет реализовать только на логических элементах. Арбитраж шин (централизованный параллельный) так же как и предсказатель переходов (4 бита, шаблон – исключающее “ИЛИ” IP и GHR ) будут реализованы отдельно, т.к. разрабатываемая микро-ЭВМ будет не конвейеризированная, а лишь многотактовая (подразумевается процессор).

Стек будет реализован отдельным блоком и с направлением роста вниз и объёмом 12 байт, ничего сложного.

Контроллер DMA задан объёмом 8 байт с начальным адресом 0xF в памяти RAM, с ним придётся повозиться, т.к. в предыдущем семестре на лабораторных подобного блока не разрабатывалось и заготовки отсутствуют.

ВВЕДЕНИЕ…………...………………………………………….………....….4

1 РАЗРАБОТКА ОБЩЕЙ СТРУКТУРЫ МИКРО-ЭВМ……………...........5

2.1 Функциональный состав микро-ЭВМ …………………………..…....5

2.2 Разработка системы команд ……………………………………..........7

2.3 Описание взаимодействия всех блоков микро-ЭВМ при выполнении команд программы ……………………………………...9

2 РАЗРАБОТКА ОСНОВНЫХ УСТРОЙСТВ МИКРО-ЭВМ ……………12

2.1 Запоминающее устройство ……………………..…………………….12

2.2 Устройство управления …………………………..………………….. 15

2.3 Регистры общего назначения……………………..…...……………...19

2.4 Блок общих операций………………………………..……………….. 21

2.4.1 Блок нулевой итерации ………………………..………………..23

2.4.2 Блоки арбитража к общим шинам ……………..………………24

2.4.3 Блок операции NOP (нет операции) ……………..…………….26

2.4.4 Блок операции JMP (безусловный переход) ……..…………... 28

2.4.5 Блок операции М->R (чтение из RAM в РОН) ……..…………30

2.4.6 Блок операции R->M (запись из РОН в RAM) ………,.……… 32

2.5 Арифметико-логическое устройство …………………………..…….34

2.5.1 Блоки арбитража к общим шинам …………………………..…36

2.5.2 Блок регистров арифметико-логического устройства……..….38

2.5.3 Блок операции ROR (циклический сдвиг вправо)…………..... 39

2.5.4 Блок операции ADDC (сложение с переносом)……………..... 41

2.5.5 Блок операции INCS (инкремент по флагу S)……………….... 43

2.5.6 Блок операции NOT (побитовое инвертирование)……..……...45

2.5.7 Блок операции AND (побитовое «И»)……………..…………...47

2.6 Стековое запоминающее устройство……………………..…………..49

2.6.1 Блоки арбитража к общим шинам…………………..…………..50

2.6.2 Блок схемы стека……………………………………..…………. 51

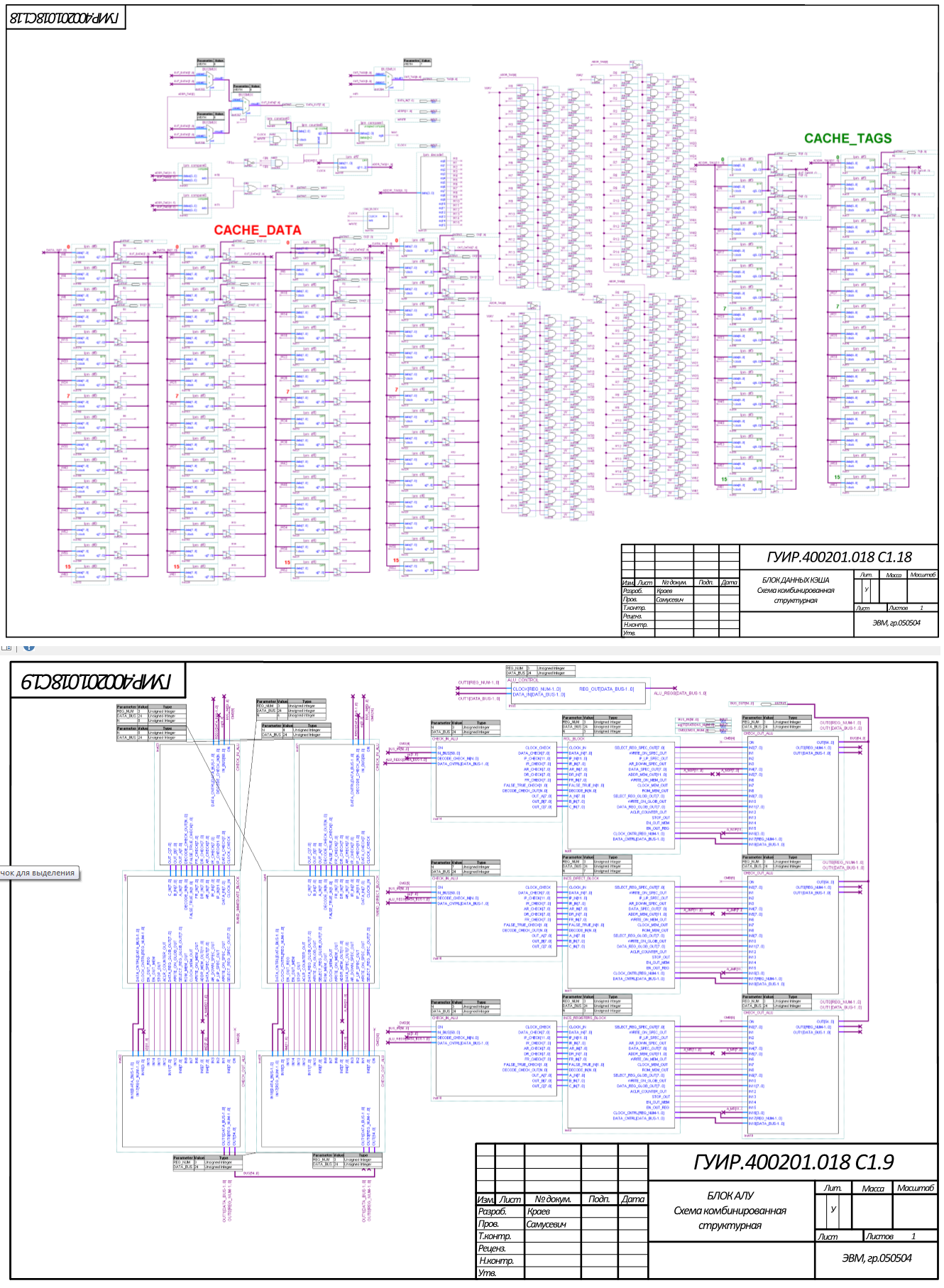

2.7 КЭШ-память………………………………………………...…………..54

2.7.1 Блок данных КЭШа…………………………………..…………. 56

2.7.2 Второстепенные блоки КЭШа………………………..…………61

2.7.3 Блок управления КЭШа………………………………..………...63

2.8 Контроллер прямого доступа к памяти………………………..……...79

2.9 Предсказатель переходов………………………………………..……. 82

2.10 Организация арбитража……………………………………..…...85

3 ПОЛНАЯ ВРЕМЕННАЯ ДИАГРАММА ФУНКЦИОНАЛЬНОГО МОДЕЛИРОВАНИЯ РАБОТЫ МИКРО-ЭВМ И ЕЁ АНАЛИЗ ….….….87

ЗАКЛЮЧЕНИЕ ………………………….………………………………...…..90

СПИСОК ЛИТЕРАТУРЫ.…………….…………………………………..…..91

ПРИЛОЖЕНИЕ А Система команд микро-ЭВМ…………………….…..….92

Выполнена в Quartus II 9.1 Altera Complete Design Suite 9.1

Используя функцию входа через сторонние сервисы, Вы соглашаетесь на обработку персональных данных в соответствии с Политикой конфиденциальности