Тульский государственный университет

Кафедра приборы управления

Курсовая работа по дисциплине "Микропроцессорная техника"

На тему: "Разработка арифметико-логического устройства"

Тула 2016

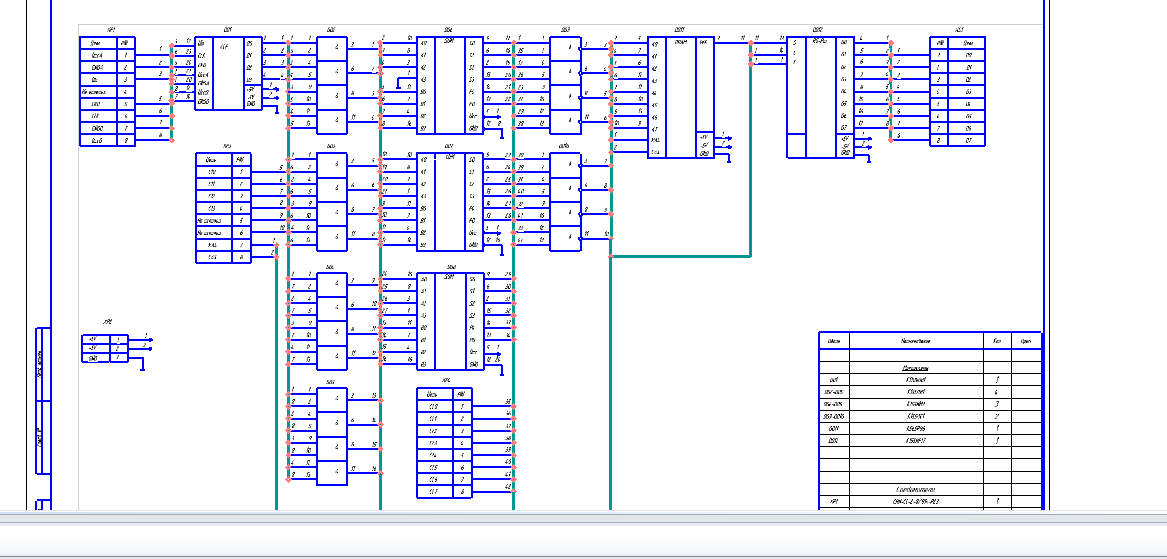

Вариант 3

Содержание

Введение…………………………………………………………………………..3

1. Исходные данные …………………………………………………………5

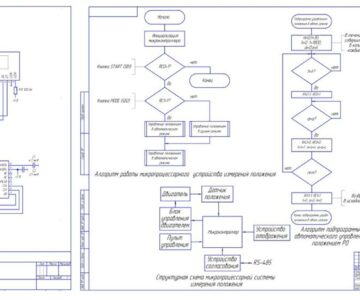

2. Принцип работы…………………………………………………………..6

3. Источник данных…………………………………………………………..6

4. Матричный умножитель………………………………………………….8

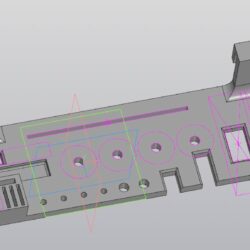

5. Схема включения элементов для реализации матричного

умножителя …………………………………………………………………10

6. Логическая операция «И-Не»……………………………………………11

7. Приемник данных ………………………………………………………12

8. Двенадцатиразрядный регистр последовательного приближения ...13

9. Электрические соединители ……………………………………………15

Заключение …………………………………………………………………….16

Список используемой литературы …………………………………………..17

Исходные данные:

Источник данных - К1108ПВ1

Арифметическая операция - Умножение

Разрядность разъема 1 - 4 матричный

Логическая операция - И-Не

Разрядность разъема 2 - Выбирается самостоятельно по разрядности выходных данных после арифметической операции

Приемник данных - К565РУ6

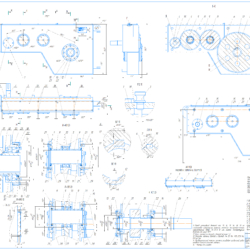

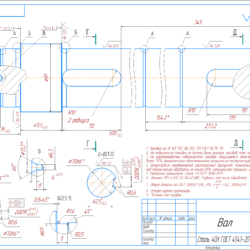

Графическая часть содержит принципиальную электрическую схему устройства

Используя функцию входа через сторонние сервисы, Вы соглашаетесь на обработку персональных данных в соответствии с Политикой конфиденциальности